#### UNIVERSITY OF UDINE

Bachelor's Degree in Multimedia Science and Technology

# Retrocomputing on PlayStation 1: design and development of two Tech Demos for the console's 30th anniversary

**Supervisor:** Demis Ballis **Student:** Gabriele Passuello

**Student ID:** 157724

# **Contents**

| Al | Abstract in Italian |          |                                        |    |  |  |

|----|---------------------|----------|----------------------------------------|----|--|--|

| Al | ostrac              | et       |                                        | 2  |  |  |

| Ι  | Or                  | igins a  | and Hardware of PlayStation            | 4  |  |  |

| 1  | The                 | sis Obje | ective                                 | 5  |  |  |

| 2  | The                 | Birth o  | of PlayStation                         | 7  |  |  |

|    | 2.1                 | Ken K    | utaragi                                | 7  |  |  |

|    | 2.2                 | The Ea   | arly Collaborations: Sony and Nintendo | 8  |  |  |

|    | 2.3                 | PS-X     |                                        | 8  |  |  |

|    | 2.4                 | The Bi   | irth of Sony Computer Entertainment    | 10 |  |  |

|    | 2.5                 |          | t Assertion                            | 11 |  |  |

| 3  | The                 | Hardw    | are of PlayStation                     | 13 |  |  |

|    | 3.1                 | The M    | odels                                  | 13 |  |  |

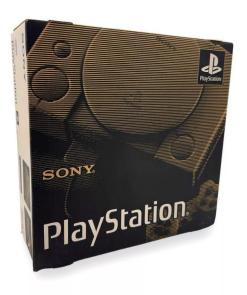

|    |                     | 3.1.1    | The SCPH-1000 Model                    | 14 |  |  |

|    |                     | 3.1.2    | The SCPH-3000 Model                    | 16 |  |  |

|    |                     | 3.1.3    | The SCPH-5000 Model                    | 17 |  |  |

|    |                     | 3.1.4    | The SCPH-7000 Model                    | 18 |  |  |

|    |                     | 3.1.5    | The SCPH-9000 Model                    | 19 |  |  |

|    |                     | 3.1.6    | The SCPH-100 Model                     | 19 |  |  |

|    |                     | 3.1.7    | The DTL-H Models                       | 20 |  |  |

|    | 3.2                 | Hardw    | vare Overview                          | 21 |  |  |

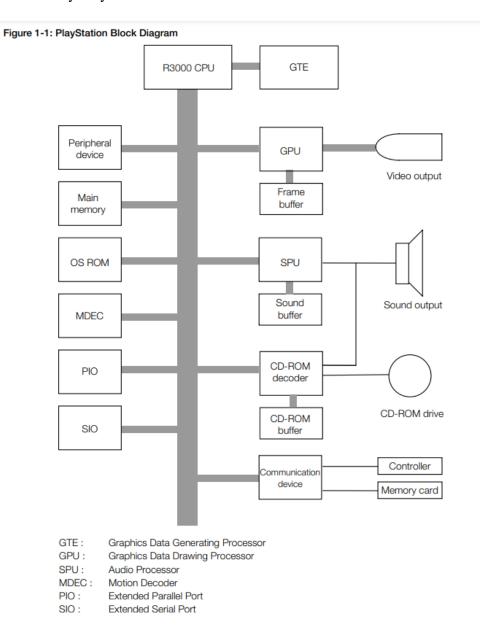

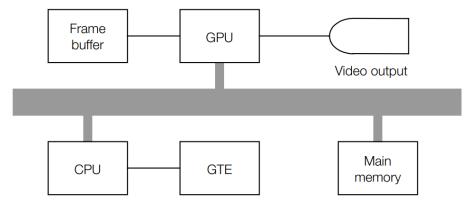

|    |                     | 3.2.1    | System Architecture                    | 22 |  |  |

|    |                     | 3.2.2    | CPU Introduction                       | 23 |  |  |

|    |                     | 3.2.3    | Graphics System Introduction           | 23 |  |  |

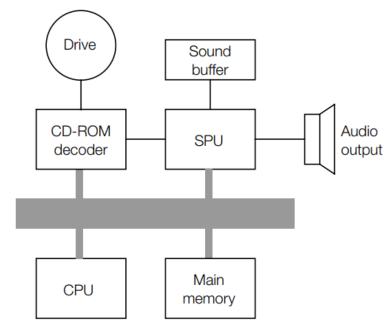

|    |                     | 3.2.4    | Audio System Introduction              | 24 |  |  |

|    |                     | 3.2.5    | Additional Supports                    | 25 |  |  |

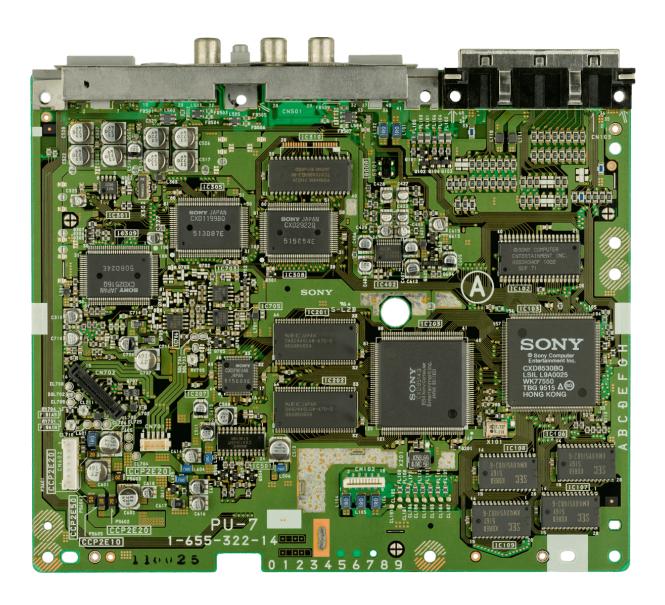

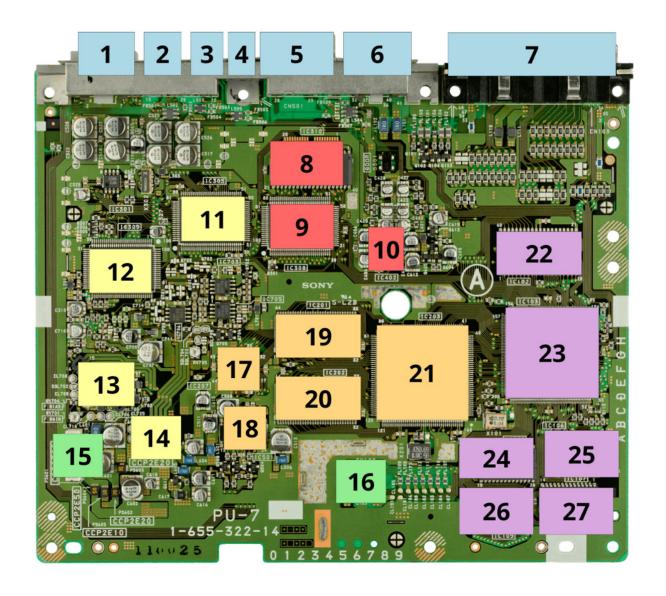

|    |                     | 3.2.6    | Motherboard Analysis                   | 26 |  |  |

|    | 2.2                 | The D    | ON COLL                                | 20 |  |  |

|    |     | 3.3.1   | Processor Characteristics                | 28 |

|----|-----|---------|------------------------------------------|----|

|    |     | 3.3.2   | Processor Origins                        | 29 |

|    |     | 3.3.3   | Coprocessors Analysis                    | 31 |

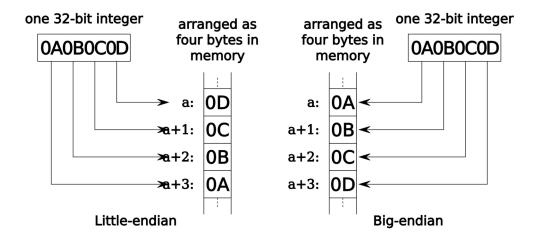

|    |     | 3.3.4   | Memory with Addressable Access           | 32 |

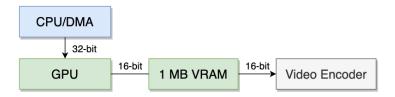

|    | 3.4 | The PS  | SX GPU                                   | 35 |

|    |     | 3.4.1   | VRAM                                     | 36 |

|    |     | 3.4.2   | Video Outputs                            | 36 |

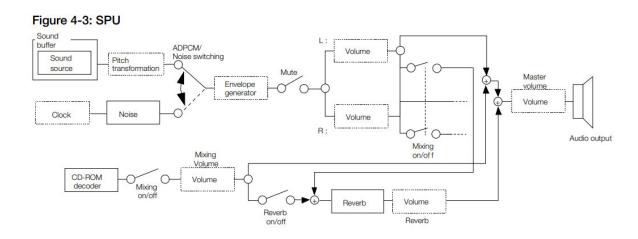

|    | 3.5 | The PS  | SX SPU                                   | 37 |

|    | 3.6 | Manag   | gement of PSX I/O Interfaces             | 38 |

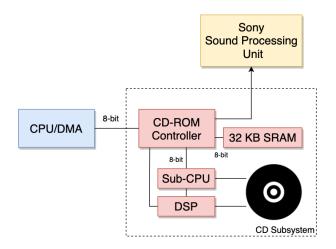

|    |     | 3.6.1   | CD Module                                | 38 |

|    |     | 3.6.2   | Front Ports                              | 39 |

|    |     | 3.6.3   | Rear Ports                               | 39 |

|    |     |         |                                          |    |

| II | De  | evelopi | ment and Programming Fundamentals on PS1 | 40 |

|    |     | -       |                                          |    |

| 4  | _   |         | ng in MIPS Assembly                      | 41 |

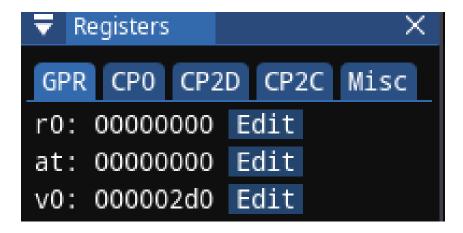

|    | 4.1 |         | General-Purpose Registers                | 41 |

|    | 4.2 |         | ntary MIPS Instructions                  | 43 |

|    |     | 4.2.1   | Data Transfer Instructions               | 43 |

|    |     | 4.2.2   | Load Instructions                        | 44 |

|    |     | 4.2.3   | Store Instructions                       | 45 |

|    |     | 4.2.4   | Differences between Load and Store       | 45 |

|    |     | 4.2.5   | Jump Instructions                        | 45 |

|    |     | 4.2.6   | Branch Instructions                      | 46 |

|    |     | 4.2.7   | The NOP Concept                          | 46 |

|    |     | 4.2.8   | Arithmetical Instructions                | 47 |

|    | 4.3 |         | le Emulation                             | 48 |

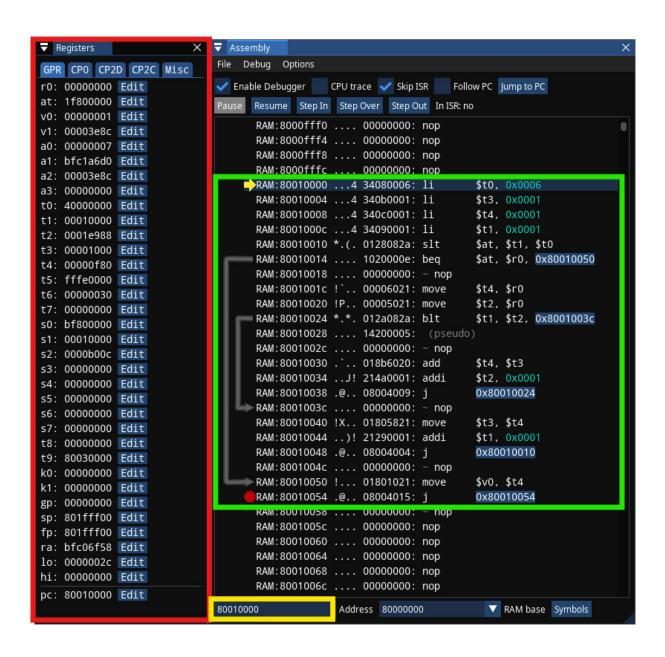

|    |     | 4.3.1   | Programming Example                      | 48 |

|    |     | 4.3.2   | The PS-EXE Format                        | 49 |

|    |     | 4.3.3   | The Pseudo-Instruction Concept           | 51 |

|    |     | 4.3.4   | The Sub-Routine Concept                  | 51 |

|    | 4.4 |         | ng Binary Data                           | 52 |

|    |     | 4.4.1   | Managing Negative Numbers                | 52 |

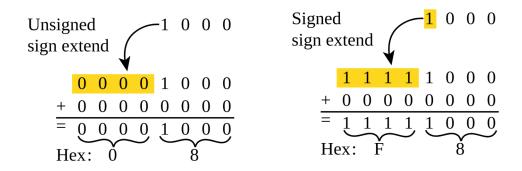

|    |     | 4.4.2   | Sign Extension                           | 53 |

|    |     | 4.4.3   | Logical Operations                       | 54 |

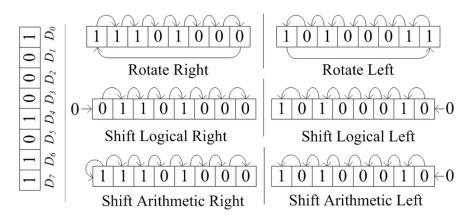

|    | 4.7 | 4.4.4   | The Bit-Shifting Concept                 | 55 |

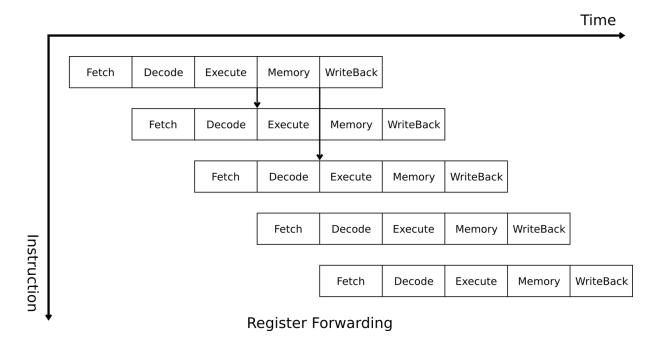

|    | 4.5 |         | th Study of the MIPS Pipeline            | 57 |

|    |     | 4.5.1   | MIPS Pipeline Structure                  | 57 |

|   |      | 4.5.2  | Limits of the MIPS Pipeline                             | 58 |

|---|------|--------|---------------------------------------------------------|----|

|   |      | 4.5.3  | Managing Delay Slots                                    | 58 |

|   |      | 4.5.4  | Optimizing Delay Slots                                  | 58 |

|   | 4.6  | In-dep | oth Study of the RISC Processor                         | 58 |

|   |      | 4.6.1  | Historical Evolution and Context                        | 58 |

|   |      | 4.6.2  | Differences between RISC and CISC                       | 59 |

|   |      | 4.6.3  | Advantages of RISC Architecture                         | 60 |

|   | 4.7  | Graph  | ics System                                              | 60 |

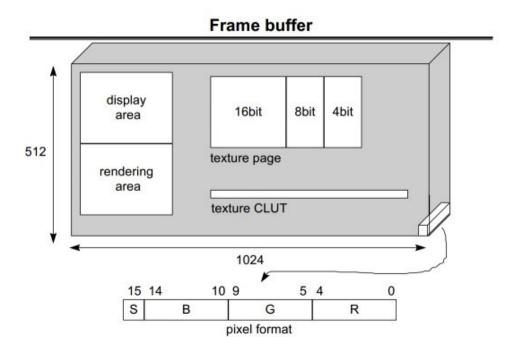

|   |      | 4.7.1  | The Frame Buffer                                        | 61 |

|   |      | 4.7.2  | Display Configuration Parameters                        | 62 |

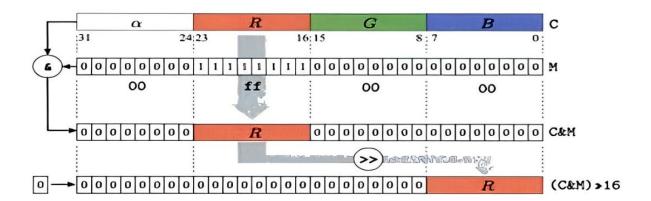

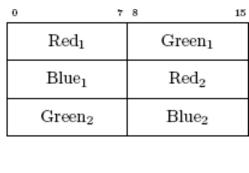

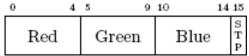

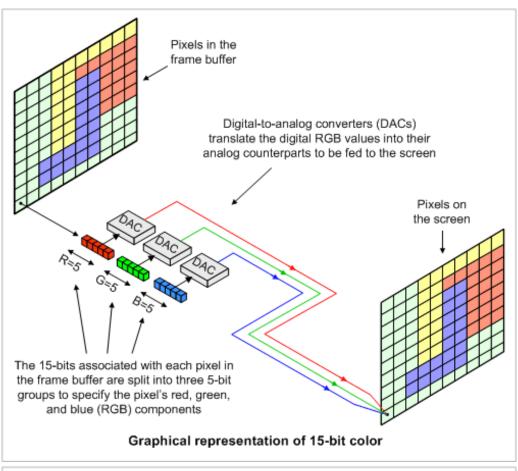

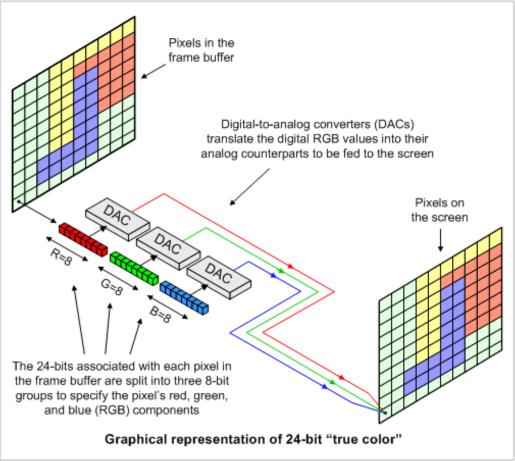

|   |      | 4.7.3  | Color and Depth                                         | 63 |

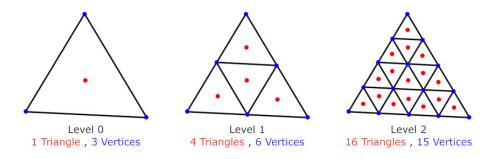

|   |      | 4.7.4  | PSX Primitives                                          | 66 |

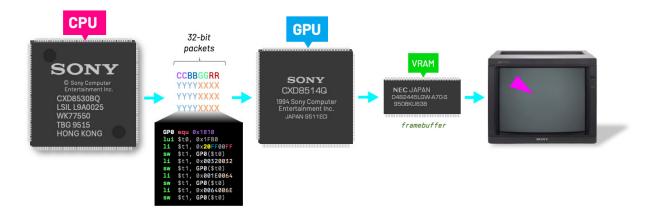

|   |      | 4.7.5  | Packet Management and Communication between CPU and GPU | 67 |

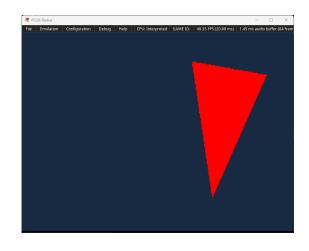

|   |      | 4.7.6  | First Example of Basic Rendering in MIPS Assembly       | 68 |

|   | 4.8  | Memo   | ory Management                                          | 73 |

|   |      | 4.8.1  | The MIPS Application Binary Interface                   | 73 |

|   |      | 4.8.2  | The Concepts of Heap and Stack                          | 74 |

|   |      | 4.8.3  | Second Example of Basic Rendering in MIPS Assembly      | 75 |

|   |      | 4.8.4  | The Concept of Variable and Vector Alignment            | 77 |

|   |      | 4.8.5  | Third Example of Basic Rendering in MIPS Assembly       | 78 |

| 5 | Prog | grammi | ing in C                                                | 84 |

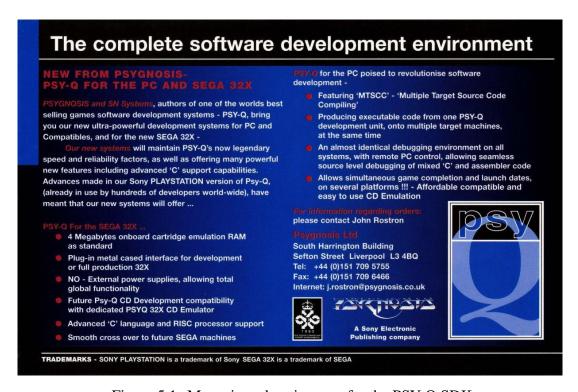

|   | 5.1  | Histor | y of the PSY-Q SDK                                      | 85 |

|   | 5.2  | Key Pı | rogramming Concepts                                     | 86 |

|   |      | 5.2.1  | Double Buffering                                        | 86 |

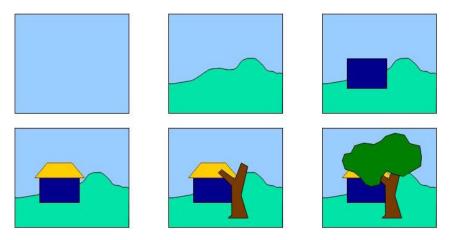

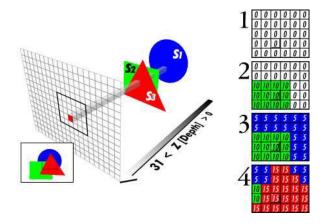

|   |      | 5.2.2  | Z-Sorting                                               | 86 |

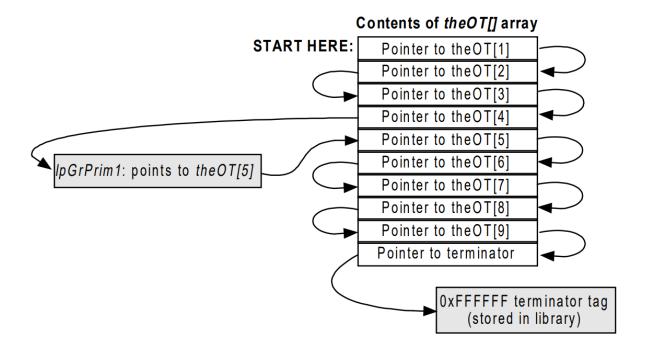

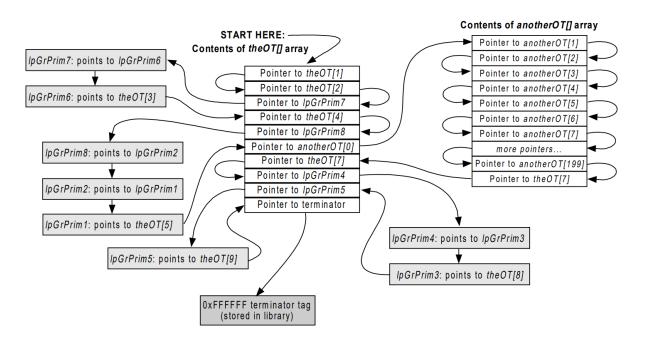

|   |      | 5.2.3  | Ordering Tables                                         | 86 |

|   | 5.3  | Main S | System Libraries                                        | 89 |

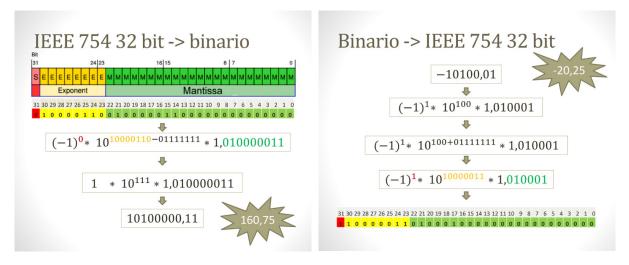

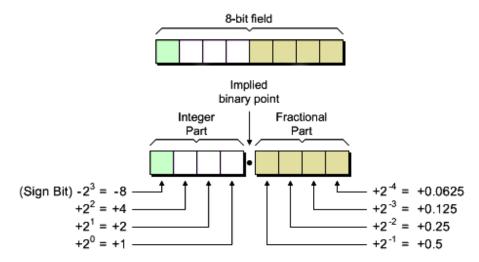

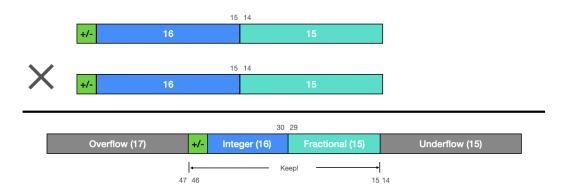

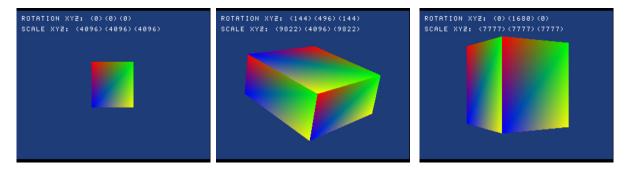

|   | 5.4  | Geome  | etry Transformation Engine                              | 90 |

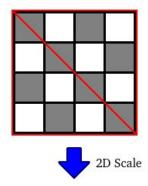

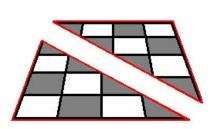

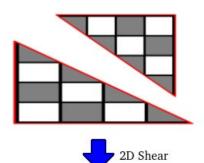

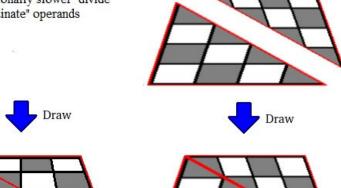

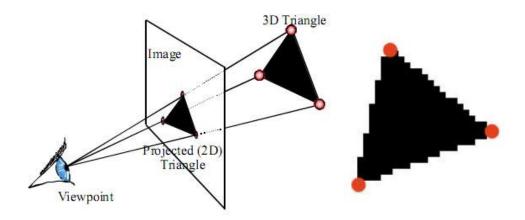

|   |      | 5.4.1  | 3D Transformations                                      | 90 |

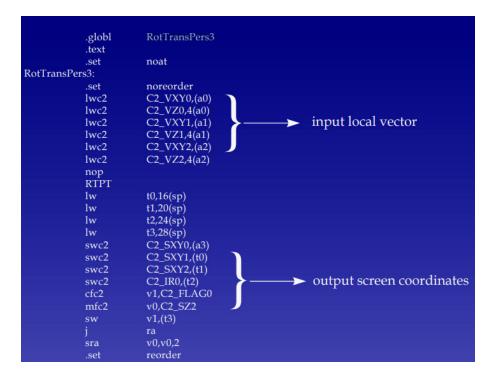

|   |      | 5.4.2  | Examples of GTE Instructions                            | 91 |

|   |      | 5.4.3  | GTE Register Set                                        | 94 |

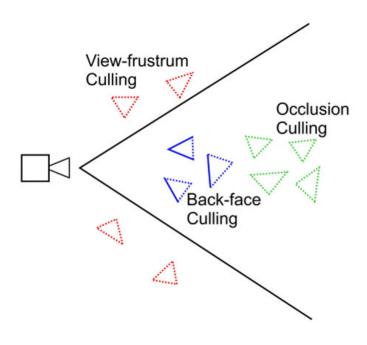

|   | 5.5  | Clippi | ng                                                      | 96 |

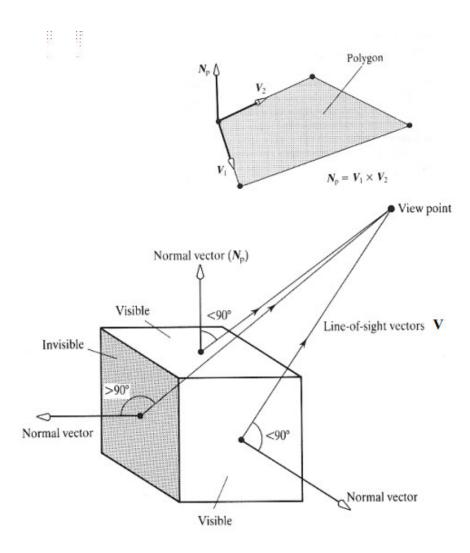

|   |      | 5.5.1  | Backface Culling                                        | 96 |

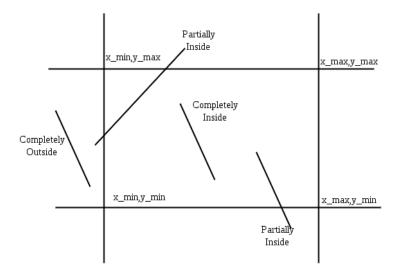

|   |      | 550    | Cohen-Sutherland Algorithm                              | 98 |

|   |      | 5.5.2  |                                                         |    |

|   |      | 5.5.3  | -                                                       | 99 |

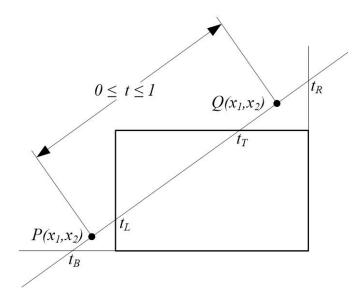

|   |      |        | Liang-Barsky Algorithm                                  |    |

|           | 5.7                                                                       | In-depth Analysis of the PSX BIOS                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |

|-----------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

|           |                                                                           | 5.7.1                                                                     | Reading Joypad Inputs via BIOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 106                                                 |

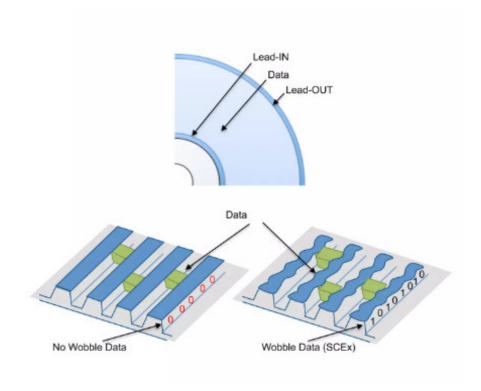

|           | 5.8                                                                       | Readin                                                                    | g the CD-ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 107                                                 |

|           |                                                                           | 5.8.1                                                                     | CD-ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 107                                                 |

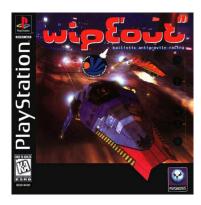

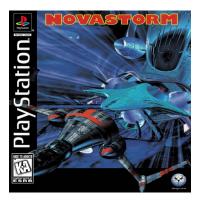

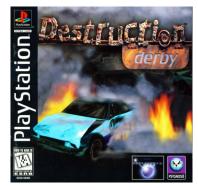

|           |                                                                           | 5.8.2                                                                     | The Unique Design of PSX CDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 110                                                 |

|           |                                                                           | 5.8.3                                                                     | Types of PlayStation Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 110                                                 |

|           |                                                                           | 5.8.4                                                                     | Function to Read Binary Data from the Disc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 112                                                 |

|           |                                                                           | 5.8.5                                                                     | Anti-Piracy Mechanisms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 113                                                 |

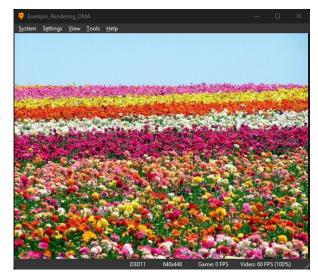

|           | 5.9                                                                       | Texture                                                                   | es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 115                                                 |

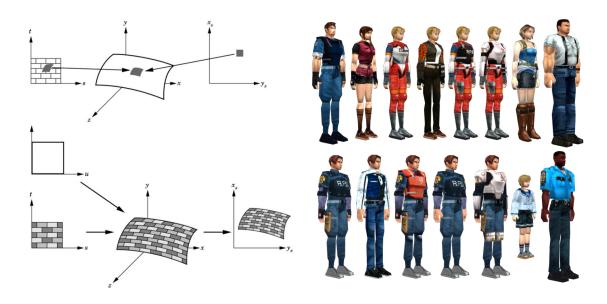

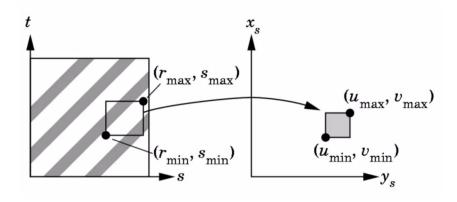

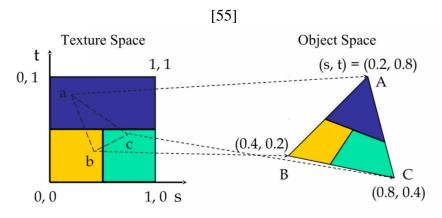

|           |                                                                           | 5.9.1                                                                     | Foundations of Texture Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 115                                                 |

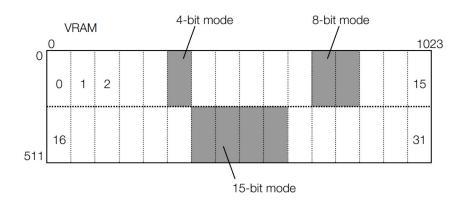

|           |                                                                           | 5.9.2                                                                     | Concept of T-PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 118                                                 |

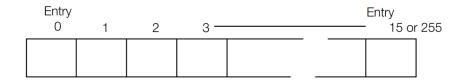

|           |                                                                           | 5.9.3                                                                     | Concept of CLUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 119                                                 |

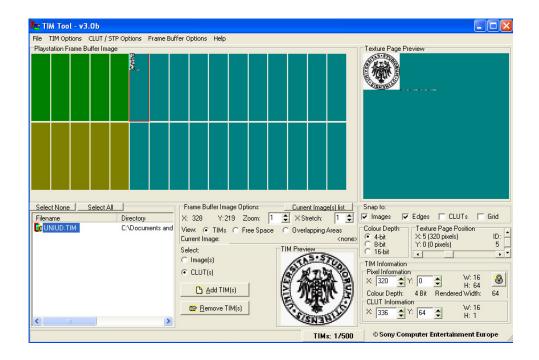

|           |                                                                           | 5.9.4                                                                     | Insight on the TIM format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 119                                                 |

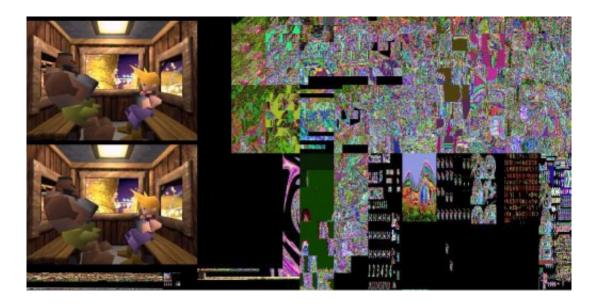

|           |                                                                           | 5.9.5                                                                     | PSX Graphic Artifacts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 120                                                 |

|           | 5.10                                                                      | Audio                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 124                                                 |

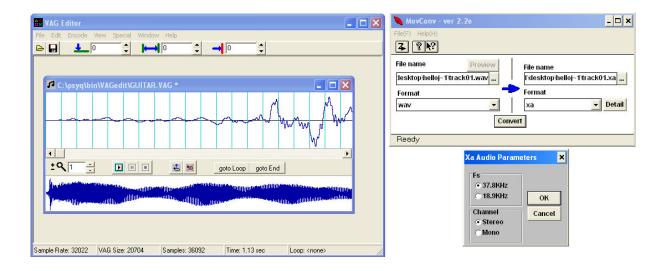

|           |                                                                           | 5.10.1                                                                    | Types of ADPCM formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 124                                                 |

|           |                                                                           | 5.10.2                                                                    | Details on VAG and XA formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 125                                                 |

|           |                                                                           | 5.10.3                                                                    | Management of Audio Tracks on CD-ROMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 127                                                 |

|           |                                                                           | 5.10.4                                                                    | Example of audio implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 129                                                 |

|           |                                                                           | 2.10.1                                                                    | r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |

|           |                                                                           | 5.10.1                                                                    | r r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                     |

| П         | ı C                                                                       |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |

| II        |                                                                           |                                                                           | g Demos on PlayStation: A Technical and Creative Show-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     |

| III<br>ca |                                                                           |                                                                           | g Demos on PlayStation: A Technical and Creative Show-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 30                                                  |

| ca        | se                                                                        | reatin                                                                    | g Demos on PlayStation: A Technical and Creative Show-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     |

| ca        | se                                                                        | reatin                                                                    | g Demos on PlayStation: A Technical and Creative Show-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>30</b>                                           |

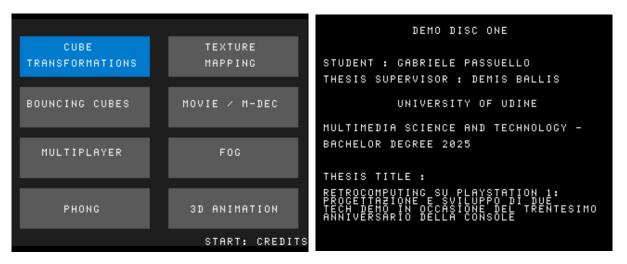

| ca        | se<br>Dem                                                                 | reatin  o Disc (                                                          | g Demos on PlayStation: A Technical and Creative Show-  1 One (Showcase of Various Demos)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>30 131</b> 131                                   |

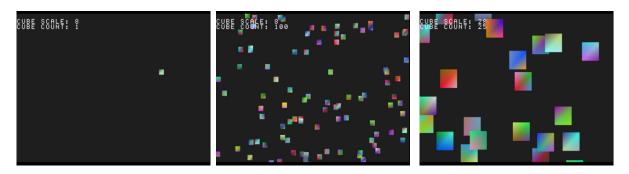

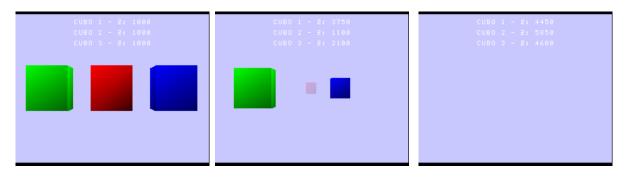

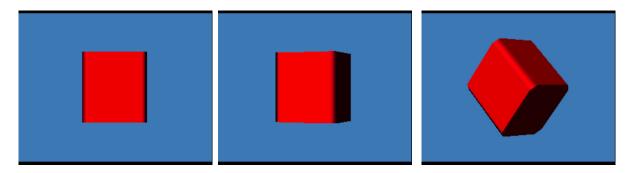

| ca        | <b>Dem</b> 6.1                                                            | reatin  o Disc ( Cube T  Bounci                                           | g Demos on PlayStation: A Technical and Creative Show-  1 One (Showcase of Various Demos)  Transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>30 131 131 132</b>                               |

| ca        | Dem<br>6.1<br>6.2                                                         | reatin  o Disc ( Cube T  Bounci                                           | g Demos on PlayStation: A Technical and Creative Show-  1 One (Showcase of Various Demos)  Transformations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>30 131 131 132 133</b>                           |

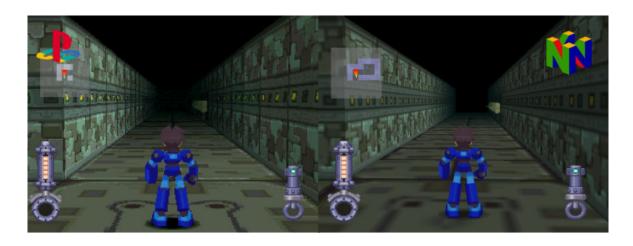

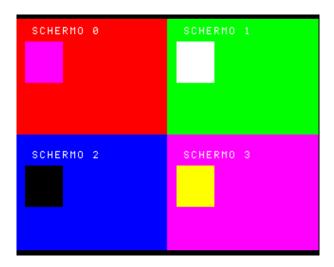

| ca        | Dem<br>6.1<br>6.2<br>6.3                                                  | co Disc (Cube To Bouncier Multip                                          | g Demos on PlayStation: A Technical and Creative Show-  1 One (Showcase of Various Demos)  Transformations  ing Cubes  layer  1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>30 131 131 132 133 134</b>                       |